# Study of Improved Topologies of Nanowire MOSFET: Solution to Doping Control Issues

Krishan Kumar<sup>1</sup> and Ashish Raman<sup>2</sup> <sup>1-2</sup>Dr.B.R.Ambedkar National Institute of Technology, Jalandhar, India Email: krishangarg2011@gmail.com, ramana@nitj.ac.in

Abstract—As we know that technology is improving day by day, due to this the number of transistors on chip should be doubled every year as per "Moore's Law". Hence, the size of transistor should be reduced to follow this scaling trend but using conventional planar MOSFET we cannot reduce the size of transistor to a limit. This is happened because of short channel effects (SCEs), which degrades MOSFET performance at lower dimensions. But there are many alternate structures like nanotube, nanowire, graphene etc. which will help in reducing the size of transistor by offering lower SCEs. In this paper, we will discuss about various types of nanowire MOSFETs and their analog performances like  $I_{\rm ON}$ ,  $I_{\rm OFF}$ ,  $U_{\rm ON}/I_{\rm OFF}$  current ratio. Beside this, an in depth review of doping control issues and the possible solutions in the nanowire MOSFETs are also presented.

Index Terms- nanowire, short channel effects.

## I. INTRODUCTION

There are various short channel effects like leakage current, heat dissipation, band to band tunneling, gate induced drain leakage effects develop in MOSFET due to scaling down MOSFET in nanometer regime [1]. These effects are reduced by nano-scaled devices like nanowire. Nanowire (NW) MOSFET has various advantages over bulk MOSFET such as less power dissipation, higher speed and higher packaging density [2]. We know that with increase in number of gate in MOSFET, electrostatic control over channel increases, hence nanowire has highest electrostatic control over channel due to having multi gate structure [2]. There are two approaches for fabricating nanowire (1) top-bottom approach (2) bottom-top approach. Top-bottom approach is done by advanced lithography with dry/wet etching whereas bottom-top approach is done by chemical vapour deposition (CVD). Bottom-up approach for fabricating nanowire has higher advantages over top-bottom approach like cost effective and higher quality [2]. Nanowire has been researched on both junction based and junctionless devices [3,8,9]. Junction based nanowire MOSFET has abrupt junction between drain/source and silicon body [5]. Due to ultrasharp junction creation between source/drain and silicon body, magnitude of doping concentration in junction based device changes with distance of some nananometer [14]. Hence there is a need of ultrafast dopant activation process and highly precise doping techniques. Junctionless nanowire MOSFET is free from junctions and has constant doping concentration in source, channel and drain areas [10-13]. Junction based nanowire MOSFET comes under category of inversion-mode MOSFET whereas junctionless nanowire MOSFET uses the mechanism for carrier transportation that why junctionless nanowire MOSFET termed as accumulation-mode MOSFET [5].

*Grenze ID: 01.GIJET.6.2.7* © *Grenze Scientific Society, 2020*  Junctionless device has lots of advantages over junction based device like excellent short channel immunity and less OFF current [10,15,16,17,18]. but because of using highly doping concentration in source, drain and channel, junctionless device suffers from random dopant fluctuation (RDF) effects like threshold voltage variations [4], subthreshold swing and variation in analog performance like decrease mobility of carrier, decrease on-state ( $I_{ON}$ ) current [7], decrease transconductance [7,19,20]. To solve these problems, charge plasma based dopingless nanowire MOSFET is proposed. Charged plasma technique uses appropriate work function of source, drain and gate metal electrode as well as lightly doping on silicon body for the formation of source/drain region whereas in junctionless device, accumulation of electrons at edge of source and drain region are done by using heavy doping in silicon body as well as appropriate work function.

Charge plasma technique has already proposed for various other devices like bipolar junction transistor [23] and p-n junction diode [21]. There are great advantages of using charge plasma technique like reduction in fabrication cost and thermal budget [25]. Shan et al. [24] showed the fabrication processing steps for charge plasma based MOSFET [4].

In this paper, various improved topologies of nanowire MOSFET is discussed and compared. Different improved topologies will help in to solve doping control issues as well as enhance analog performances like increased ION current, reduced IOFF current and subthreshold slope etc. In the second section of this paper, conventional junction based nanowire is discussed. In the third section, improved structure of nanowire is discussed which is used to reduce doping problems. In the forth section conclusion of this paper is discussed.

## II. CONVENTIONAL JUNCTION BASED NANOWIRE

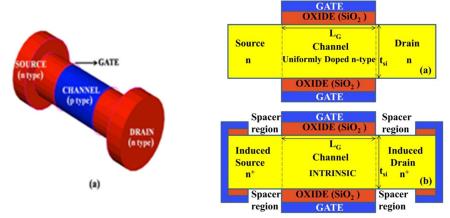

Conventional Junction based nanowire is inversion-mode MOSFET [5]. From study of Ref. [3], it is found that conventional junction based nanowire uses channel doping of  $1 \times 10^{14}$  cm<sup>-3</sup> whereas source/drain doping of  $1 \times 10^{20}$  cm<sup>-3</sup> [3]. Remaining parameter i.e. body thickness = 32 nm and channel length = 45 nm [3]. 3D structure for conventional device is shown in Fig.1. Analog performance for the device like that ION current and IOFF current for conventional junction based nanowire is  $3.09 \times 10^{-3}$  A and  $1.04 \times 10^{-7}$  A at gate work function of 4.4 eV [3]. Moreover, due to have abrupt junctions and variation in doping concentration between drain, source and channel, conventional device has high series resistance [5] which reduced overall performance of device. Therefore, there are many devices have been designed to solve the problem of doping control and abrupt junctions. These types of improved devices will be discussed in next section.

III. IMPROVED STRUCTURES TO CONTROL DOPING PROBLEMS AND ENHANCE ANALOG PERFORMANCE

## A. Junctionless and Dopingless Nanowire MOSFET

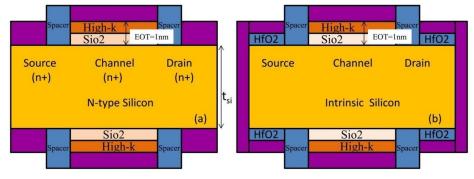

Fig. 2 shows the 2D cross-section view of junctionless and dopingless nanowire MOSFET [4]. From study of Ref. [4], it is found that channel/drain/source doping for both device junctionless nanowire and dopingless nanowire is  $1 \times 10^{19}$  cm<sup>-3</sup>, and  $1 \times 10^{15}$  cm<sup>-3</sup> respectively whereas remaining parameter for both device remains same such as body thickness is 10nm ,length of channel is 20nm [4]. Both junctionless and dopingless nanowire mosfets are the accumulation-mode MOSFET. In both devices source and drain regions induced by accumulation of electron. In dopingless nanowire MOSFET, accumulation of electron is done by charge plasma concept. Due to having uniform doping concentration between source/drain and channel, these devices have no abrupt junction formation hence reduce series resistance as well as analog performances are such that ION current for both devices junctionless nanowire MOSFET and dopingless nanowire MOSFET

is  $\sim 10^{-5}$  A at gate work function of 5.1 eV and 4.8 eV respectively [4].

IOFF current for both devices junctionless nanowire MOSFET and dopingless nanowire MOSFET is ~  $10^{-14}$  A and ~ $10^{-15}$  A at gate work function of 5.1 eV and 4.8 eV respectively [4]. ION/IOFF current ratio for junctionless and dopingless nanowire MOSFET is 6.29 x  $10^8$  A and 3.23 x  $10^9$  A respectively at body thickness of 10 nm [4].

## B. Gate Stacked Junctionless and Dopingless Nanowire MOSFET

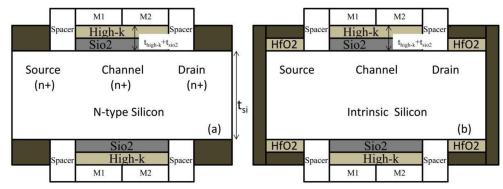

Fig. 3 shows 2D cross-sectional view of gate stacked junctionless nanowire MOSFET and gate stacked dopingless nanowire MOSFET. From Ref. [5], device structure parameters used for both devices are such as, length of gate is 20 nm, body thickness is 10 nm, spacer length is 10 nm, doping concentration used for gate

Figure 1(a) 3D structural view of conventional

Figure 2. 2D cross-sectional view of (a) Junctionless

Junction based nanowire MOSFET [3].

nanowire MOSFET (b) Dopingless nanowire MOSFET [4].

stacked junctionless and dopingless nanowire is  $1 \times 10^{19}$  cm<sup>-3</sup>, and  $1 \times 10^{15}$  cm<sup>-3</sup> respectively. In the paper Ref. [4], only oxide material is used in gate which cannot control static power dissipation and leakage current in device but from study of Ref. [5], it is observed that a high-k material is added under gate metal electrode and above oxide layer in sandwich like structure helps to reduce leakage current and power dissipation by reducing formation of gate capacitance [5].HfO2 material is also under drain and source metal electrode to reduce silicide formation [5]. Analog performances for both devices are such that ION current for both devices gate stacked junctionless nanowire MOSFET and gate stacked dopingless nanowire MOSFET is ~  $2 \times 10^{-5}$  A and ~  $6 \times 10^{-5}$  A at gate work function of 4.7 eV and 4.53 eV respectively [5]. IOFF current for both devices junctionless nanowire MOSFET and dopingless nanowire MOSFET is ~ $3 \times 10^{-10}$  A at gate work function of 4.7 eV and 4.53 eV respectively [5]. IOFF current for both devices junctionless nanowire MOSFET and dopingless nanowire MOSFET is ~ $3 \times 10^{-10}$  A at gate work function of 4.7 eV and 4.53 eV respectively [5].ION/IOFF current ratio for junctionless and dopingless nanowire MOSFET is ~ $0.6 \times 10^{5}$  A are spectively at body thickness of 5 nm. In both devices, air is used in spacer [5].

Figure 3. 2D cross-section view of (a) gate stacked junctionless nanowire MOSFET (b) gate stacked dopingless nanowire MOSFET [5]

C. Dual Material Gate and Gate Stacked Junctionless and Dopingless Nanowire MOSFET

Fig. 4 shows 2D Cross- sectional view of both devices dual material gate and gate stacked junctionless nanowire MOSFET and dual material gate and gate stacked dopingless nanowire MOSFET. From Ref. [6], structure parameter used in both devices are length of gate (LM1 +LM2 =20nm), spacer length is 10 nm, body thickness is 10 nm, doping concentration used for gate stacked junctionless and dopingless nanowire is 1x10<sup>19</sup> cm<sup>-3</sup>, and 1x10<sup>15</sup> cm<sup>-3</sup>, respectively. Dual material is used on gate metal electrode to enhance the analog performance for both devices. In both devices, work function of both material used in gate metal electrode are differ by 0.5 eV [6]. And using high-k material on top of oxide layer decreases leakage current and power dissipation by reducing formation of gate capacitances [5]. In both devices HfO2 is used under source and drain metal electrode to avoid silicide formation [5]. Analog performances are such that ION current for both devices such as dual material gate stacked junctionless nanowire MOSFET and dual material

gate stacked dopingless nanowire MOSFET is ~2 x  $10^{-4}$ A and ~4 x  $10^{-4}$  A at gate work function of M1=4.91 eV, M2=4.41 and M1=4.77 eV, M2=4.27 eV respectively [6]. IOFF current for both devices such as dual material gate stacked junctionless nanowire MOSFET and dual material gate stacked dopingless nanowire MOSFET is almost equal

i.e. ~5 x  $10^{-13}$  A at gate work function of M1=4.91 eV, M2=4.41 and M1= 4.77 eV, M2=4.27 eV respectively [6].

Figure 4. 2D cross-sectional view of (a) dual material gate and gate stacked junctionless nanowire MOSFET (b) dual material gate and gate stacked dopingless nanowire MOSFET [6]

|        |                                                          | Structure Parameters      |                           |                         |                               |                                          |                                                         | Analog Characteristics    |                            |                                   |

|--------|----------------------------------------------------------|---------------------------|---------------------------|-------------------------|-------------------------------|------------------------------------------|---------------------------------------------------------|---------------------------|----------------------------|-----------------------------------|

| S. NO  | Device                                                   | Channel<br>Length<br>(nm) | Body<br>thickness<br>(nm) | t <sub>ox</sub><br>(nm) | Gate Work<br>Function<br>(eV) | Channel<br>Doping<br>(cm <sup>-3</sup> ) | urce/drain<br>Doping (cm <sup>-</sup><br><sup>3</sup> ) | ION (A)                   | IOFF (A)                   | I <sub>ON</sub> /I <sub>OFF</sub> |

| 1.     | Conventional<br>Junction based<br>Nanowire               | 45                        | 32                        | 1                       | 4.4                           | 1x10 <sup>14</sup>                       | 1x10 <sup>20</sup>                                      | 3.09 x10 <sup>-3</sup>    | 1.04 x10 <sup>-7</sup>     | 2.98 x10 <sup>4</sup>             |

| 2. (A) | Junction less<br>Nanowire                                | 20                        | 10                        | 2                       | 5.1                           | 1x10 <sup>19</sup>                       | 1x10 <sup>19</sup>                                      | ~10 <sup>-5</sup>         | ~10-14                     | 6.29 x10 <sup>8</sup>             |

| 2. (B) | Doping Less<br>Nanowire                                  | 20                        | 10                        | 2                       | 4.8                           |                                          | 1x10 <sup>19</sup>                                      |                           | ~10-15                     | 3.23 x10 <sup>9</sup>             |

| 3. (A) | Gate<br>Stacked<br>Junction Less                         | 20                        | 10                        | 1                       | 4.7                           | 1x10 <sup>19</sup>                       | 1x10 <sup>19</sup>                                      | ~ 2<br>x 10 <sup>-5</sup> | ~ 3 <sub>x10</sub> -10     | ~ 0.6 x10 <sup>5</sup>            |

| 3. (B) | Nanowire<br>Gate Stacke<br>Doping Le<br>Nanowire         |                           | 10                        | 1                       | 4.53                          | 1x10 <sup>15</sup>                       | 1x10 <sup>15</sup>                                      | ~ 6<br>x 10 <sup>-5</sup> | ~ 1<br>x 10 <sup>-10</sup> | ~ 6 x10 <sup>5</sup>              |

| 4. (A) | Dual Materi<br>Gate Stacko<br>Junction Le<br>Nanowire    | ed20                      | 10                        | 1.1                     | 4.91,<br>4.41                 | 1 x 10 <sup>19</sup>                     | 1 x 10 <sup>19</sup>                                    |                           | ~5<br>x 10 <sup>-13</sup>  | ~0.4 x 10 <sup>9</sup>            |

| 4. (B) | Dual Material<br>Gate Stacked<br>Doping Less<br>Nanowire | 20                        | 10                        | 1.1                     | 4.77,<br>4.27                 | 1 x 10 <sup>15</sup>                     | 1 x 10 <sup>15</sup>                                    | ~4<br>x 10 <sup>-4</sup>  | ~5<br>x 10 <sup>-13</sup>  | ~0.8 x 10 <sup>9</sup>            |

| TABLE L COMPARISON OF  | VARIOUS PARAMETERS FOR   | DIFFERENT WORKS |

|------------------------|--------------------------|-----------------|

| TABLE I. COMPARISON OF | V ARIOUS I ARAMETERS FOR | DIFFERENT WORKS |

## **IV. CONCLUSIONS**

There are many studies going on day by day on nanowire MOSFET device to reduce its size, leakage current, power dissipation and SCEs thereby improve its speed and performance parameters such as ION, IOFF, ION/IOFF ratio etc. In this paper, we have summarized the various studies held on nanowire MOSFET to control its doping problem and enhance analog performance. Various researchers are now working on nanowire devices to further enhance overall performance of devices and able to sustain "Moore's Law" as nanowire structures have the potential to build future nanodevices.

## ACKNOWLEDGMENT

I would like to thank PhD scholars Sarabdeep Singh and Naveen Kumar who helped me a lot during my research work and paper writing.

#### REFERENCES

- [1] Kim, Yong-Bin. "Challenges for nanoscale MOSFETs and emerging nanoelectronics," Transactions on Electrical and Electronic Materials vol. 11, no. 3, pp. 93-105, 2010.

- [2] Zhu, H. "Semiconductor nanowire MOSFETs and applications," Nanowires New Insights, 101, 2017.

- [3] Scarlet, S.P., Ambika, R. and Srinivasan, R., "Effect of eccentricity on junction and junctionless based silicon nanowire and silicon nanotube FETs," Superlattices and Microstructures, vol. 107, pp.178-188, 2017.

- [4] Trivedi, Nitin, Manoj Kumar, Subhasis Haldar, S. S. Deswal, Mridula Gupta, and R. S. Gupta, "Charge plasma technique based dopingless accumulation mode junctionless cylindrical surrounding gate MOSFET: analog performance improvement." Applied Physics A, vol. 123, no. 9, pp. 564, 2017.

- [5] Singh, Sarabdeep, and Ashish Raman. "A dopingless gate -all around (GAA) gate -stacked nanowire FET with reduced parametric fluctuation effects." Journal of Computational Electronics vol. 17, no. 3, pp. 967-976, 2018.

- [6] Singh, Sarabdeep, and Ashish Raman. "Gate -all -around charge plasma based dual material gate -stack nanowire FET for enhanced analog performance." IEEE Transactions on Electron Devices vol. 65, no. 7, pp. 3026-3032, 2018.

- [7] Baruah, R. K., Paily, R.P.: A dual-material gate junctionless transistor with a high-k spacer for enhanced analog performance. IEEE Transactions on Electron Devices, vol. 61, no. 1, pp.123-128, 2014.

- [8] D. Tekleab, "Device performance of silicon nanotube field effect transistor," IEEE Electron Device Lett., vol. 35, no. 5, pp. 506–508, 2014.

- [9] R. Ambika and R. Srinivasan, "Performance Analysis of n-Type Junctionless Silicon Nanotube Field Effect Transistor," J. Nanoelectron. Optoelectron., vol. 11, no. 3, pp. 290–296, 2016.

- [10] J.-P. Colinge et al., "Nanowire transistors without junctions.," Nat. Nanotechnol., vol. 5, no. 3, pp. 225–229, 2010.

- [11] S. Gundapaneni, "Investigation of Junction-Less Transistor (JLT) for CMOS Scaling," Ph.d thesis, p. INDIAN INSTITUTE OF TECHNOLOGY BOMBAY, INDIA CERTI, 2012.

- [12] S. Y. Kim et al., "Design and Analysis of Sub-10 nm Junctionless Fin-Shaped Field-Effect Transistors," J. Semicond. Technol. Sci., vol. 14, no. 5, pp. 508–517, 2014. MANUSCRIPT ACCEPTED ACCEPTED MANUSCRIPT

- [13] M. H. Han, C. Y. Chang, H. Bin Chen, J. J. Wu, Y. C. Cheng, and Y. C. Wu, "Performance comparison between bulk and SOI junctionless transistors," IEEE Electron Device Lett., vol. 34, no. 2, pp. 169–171, 2013.

- [14] Doria, R.T., Pavanello, M.A., Trevisoli, R.D., de Souza, M., Lee, C.W., Ferain, I., Akhavan, N.D., Yan, R., Razavi, P., Yu, R., Kranti, A.: Junctionless multiple-gate transistors for analog applications. IEEE Trans. Electron Devices 58(8), 2511–2519 (2011)

- [15] Z. Chen, Y. Xiao, M. Tang et al., Surface-potential-based drain current model for long-channel junctionless doublegate MOSFETs. IEEE Trans. Electron Dev. 59(12), 3292–3298 (2012)

- [16] M.-H. Han, C.-Y. Chang, H.-B. Chen et al., Device and circuit performance estimation of junctionless bulk FinFETs. IEEE Trans. Electron Dev. 60(6), 1807–1813 (2013)

- [17] S. Barraud, M. Berthome, R. Coquand et al., Scaling of trigate junctionless nanowire MOSFET with gate length down to 13 nm. IEEE Electron Dev. Lett. 33(9), 1225–1227 (2012)

- [18] C.W. Lee, A.N. Nazarov, I. Ferain et al., Low subthreshold slope in junctionless multiple gate transistors. Appl. Phys. Lett. 96(2), 102106-1–102106-3 (2010)

- [19] Colinge, J.P., Kranti, A., Yan, R., Lee, C.W., Ferain, I., Yu, R., Akhavan, N.D., Razavi, P.: Junctionless nanowire transistor (JNT): properties and design guidelines. Solid-State Electron. 65, 33–37 (2011)

- [20] Rios, R., Cappellani, A., Armstrong, M., Budrevich, A., Gomez, H., Pai, R., Rahhal-Orabi, N., Kuhn, K.: Comparison of junctionless and conventional tri-gate transistors with Lg down to 26 nm. IEEE Electron Device Lett. 32(9), 1170–1172 (2011)

- [21] B. Rajasekharan, R.J.E. Hueting, C. Salm et al., Fabrication and characterization of the charge-plasma diode. IEEE

Electron Dev. Lett. 31(6), 528-530 (2010)

- [22] R.J.E. Hueting, B. Rajasekharan, C. Salm et al., Charge plasma P–N diode. IEEE Electron Dev. Lett. 29(12), 1367–1368 (2008)

- [23] M.J. Kumar, K. Nadda, Bipolar charge-plasma transistor: a novel three terminal device. IEEE Trans. Electron Dev. 59(4), 962–967 (2012)

- [24] C. Shan, Y. Wang, M.T. Bao, A charge-plasma-based transistor with induced graded channel for enhanced analog performance. IEEE Trans. Electron Dev. 63(6), 2275–2281 (2016)

- [25] C. Sahu, J. Singh, Charge-plasma based process variation immune junctionless transistor. IEEE Electron Dev. Lett. 35(3), 411–413 (2014)